ESD 基础知识

ESD(Electrostatic discharge)即静电释放。指两个物体在接近或接触时,发生的电子迅速转移的现象。众所周知,物体会在与其他物体的接触与摩擦中产生并积累电荷。比如我们的手跟外界摩擦时就会积累很多正电荷。当积累了很多正电荷的物体与一个导体距离非常近或接触的时候,电子将会快速从导体转移到积累正电荷的物体上。这个电子快速转移的过程就是静电释放(ESD)。

电子设备上通常会有很多接口,接口再通过导线连接到芯片的管脚上,然后连到芯片内部。静电释放时产生的高电压(一般高达上千伏)可能会击穿管子,如果是大电流,还可能会烧熔器件,所以要避免。

ESD 防护的关键在于为静电提供一条单独的放电通道(原理就像避雷针)。ESD 器件主要分为四类:TVS 二极管、压敏电阻、MLCC、ESD 抑制器。

ESD 测试模型

| HBM | MM | CDM | IEC 61000-4-2 MODEL | |

|---|---|---|---|---|

| 测试电压(V) | 500-2000 | 100-200 | 500-2000 | 2000-15000 |

| 脉冲时间(ns) | ~150 | ~80 | ~1 | ~150 |

| 施加 2kV 时的峰值电流(\(A_pk\)) | 1.33 | - | ~5 | 7.5 |

| 上升时间 | 25ns | - | <400ps | <1ns |

| 电压冲击次数 | 2 | 2 | 2 | 20 |

人体模型(HBM, Human Body Model)

假设由人体静电放电时的测试,模拟出人用手触摸芯片时的情况。

机器模型(MM, Machine Model)

假设由机械静电放电时的测试,模拟出通过机械手或者其他电阻较小的工具触碰芯片时发生静电释放的情形。

它与人体模型的区别在于电容更大、没有电阻,因此可想而知放电电流会大得多,而且由于导线的电感效应还会出现震荡电流,即对芯片放电的电流是正负变化的。

带电设备模型(CDM, Charged Device Model)

前两种模型模拟的都是带电体向芯片放电的情况,带电设备模型则模拟的是芯片自身带电,对地放电的情形。从在仓库存放了一段时间的包装里把芯片拿出来时会发生这种现象。这种情况下没有电阻、电容,而是芯片通过管脚直接对地放电。

ESD 参考标准

常见的 HBM 测试规格:

| 标准 | 充电电容 \(C_d (pF)\) | 放电电阻 \(R_d (Ω)\) |

|---|---|---|

| AEC-Q200-002 | 150 | 2000 |

| IEC61000-4-2 | 150 | 330 |

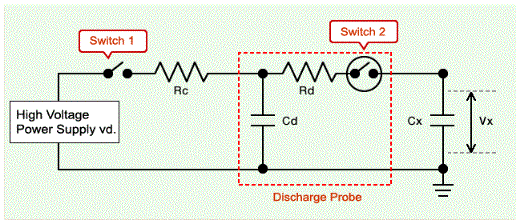

以 AEC-Q200-002 标准为例,其 ESD HBM 测试电路如下:

其中,\(C_x\) 为测试对象的电容,\(C_d\) 为充电电容,\(R_d\) 为放电电阻,\(R_c\) 为保护电阻。ESD 测试方法如下:

- 开关 1 闭合,开关 2 开路:高压电源将电荷充进 \(C_d\)

- 开关 1 开路,开关 2 闭合:\(C_d\) 中储存的电荷将施加在 \(C_x\) 上,进行 ESD 测试。

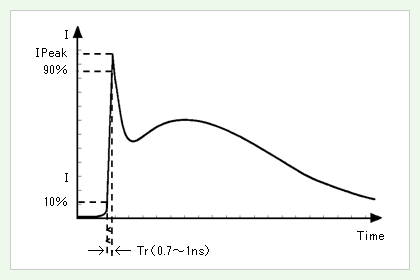

放电电流曲线:

ESD 测试流程

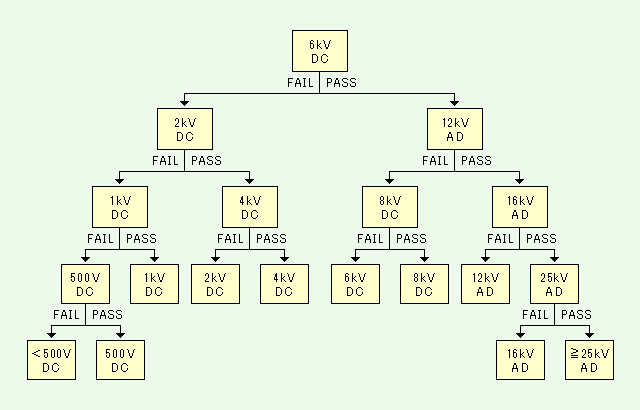

以 AEC-Q200-002 标准,HBM 测试流程可以按照下图进行:

测试出来的耐压等级按下表分类:

| 分类级别 | 最大耐压 |

|---|---|

| 1A | 小于 500V (DC) |

| 1B | 0.5 kV (DC) 以上, 小于 1 kV (DC) |

| 1C | 1 kV (DC) 以上, 小于 2 kV (DC) |

| 2 | 2 kV (DC) 以上, 小于 4 kV (DC) |

| 3 | 4 kV (DC) 以上, 小于 6 kV (DC) |

| 4 | 6 kV (DC) 以上, 小于 8 kV (DC) |

| 5A | 8 kV (DC) 以上, 小于 12 kV (AD) |

| 5B | 12 kV (AD) 以上, 小于 16 kV (AD) |

| 5C | 16 kV (AD) 以上, 小于 25 kV (AD) |

| 6 | 25 kV (AD) 以上 |

DC(Direct Contact Discharge)为直接接触放电;AD(Air Discharge)为空气放电。

测试对象的电容容值与 ESD 耐性的关系

测试对象的电容 \(C_x\) 的容值大小会影响其两端的电压,满足以下的关系:

电源电压(\(V_d\))和充电电容(\(C_d\))的容值恒定时,测试对象的电容(\(C_x\))容值的变大,会导致出现在其两侧的电压(\(V_x\))降低。

因此一般来说,\(C_x\) 的容值越大,ESD 耐性有变大的趋势。但实际上,因电介质的种类及厚度之类的设计上的差异,耐电压的性能范围也有不同,并不完全符合上述趋势。

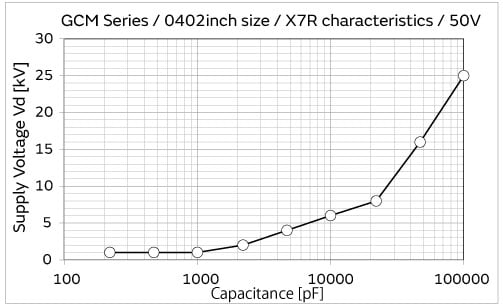

电容容值与 ESD 耐性的参考

- \(C_x\) 电容参数:GCM 系列 / 0402 封装 / X7R / 50V

- 测试条件:\(C_d=150pF,R_d=2kΩ\)

按图表曲线可得,如果我们要抵御 1kV 的 ESD,则可以用 1000pF 的电容来进行防御。在实际的电路设计中,最好给电容并联一个大电阻,在消除 ESD 后对电容里的电释放掉。

参考与致谢

原文地址:https://wiki-power.com/

本篇文章受 CC BY-NC-SA 4.0 协议保护,转载请注明出处。