بروتوكول الاتصال - مستوى الجهد الرقمي

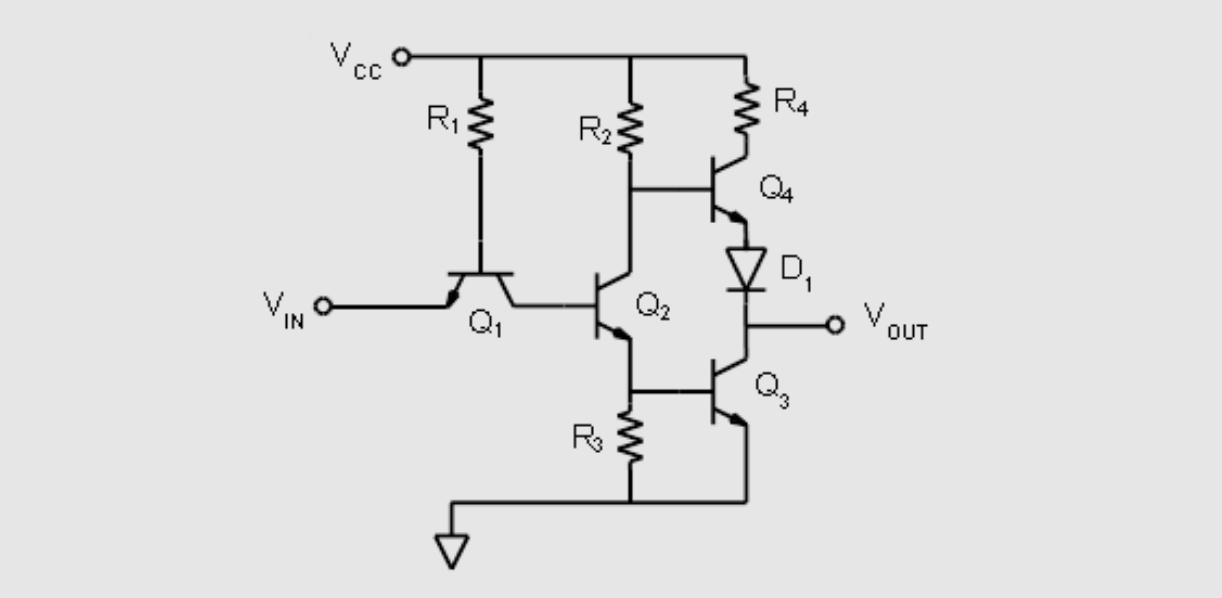

واجهة مستوى الجهد TTL

TTL (Transistor-Transistor Logic) هو مبني على هيكل ثلاثي القطبة، وتزويده القياسي بالطاقة هو 5 فولت. نظرًا للفجوة الكبيرة بين 2.4 فولت و 5 فولت، فإن التبديل المستمر للجهد يزيد من استهلاك الطاقة في النظام، لذا تم ضغطه لتشكيل مستوى LVTTL (Low Voltage Transistor-Transistor Logic)، والذي يأتي بمستويات 3.3 فولت و 2.5 فولت.

ميزات مستوى (LV) TTL:

- يتحكم الدائرة TTL في الأجهزة بواسطة التيار، وهو سريع السرعة ويتأخر قليلاً في نقل البيانات (5-10 نانوثانية)، ولكنه يستهلك الكثير من الطاقة.

- عادةً ما يكون هناك تجاوز كبير في مستوى TTL، وقد يتم توصيل مقاومة 22Ω/33Ω في الطرف البدئي.

- عندما يكون السلك المتصل بمدخل مستوى TTL معلقًا، يعتبر ذلك عالي المستوى داخليًا، وإذا كنت بحاجة إلى سحبه لأسفل، فيجب توصيل مقاومة أقل من 1 كيلو أوم للسحب.

- عادةً ما يكون سرعة واجهة مستوى TTL محدودة إلى 30 ميجاهرتز أو أقل. نظرًا لوجود سعة إدخالية صغيرة بحجم بضع بيكوفارادات في نهاية المدخل للمفتاح الثنائي القطبي الثنائي (LPF)، فإنه إذا تجاوز إشارة الإدخال ترددًا معينًا، فسيتم فقدان الإشارة.

- قدرته على التشغيل عادة ما تكون بحد أقصى عدة عشرات من المللي أمبير. يكون جهد الإشارة العاملة بشكل طبيعي عادةً مرتفعًا، وعند توصيله بدائرة ECL ذات جهد إشارة أقل، ستحدث مشكلة واضحة من التشويش.

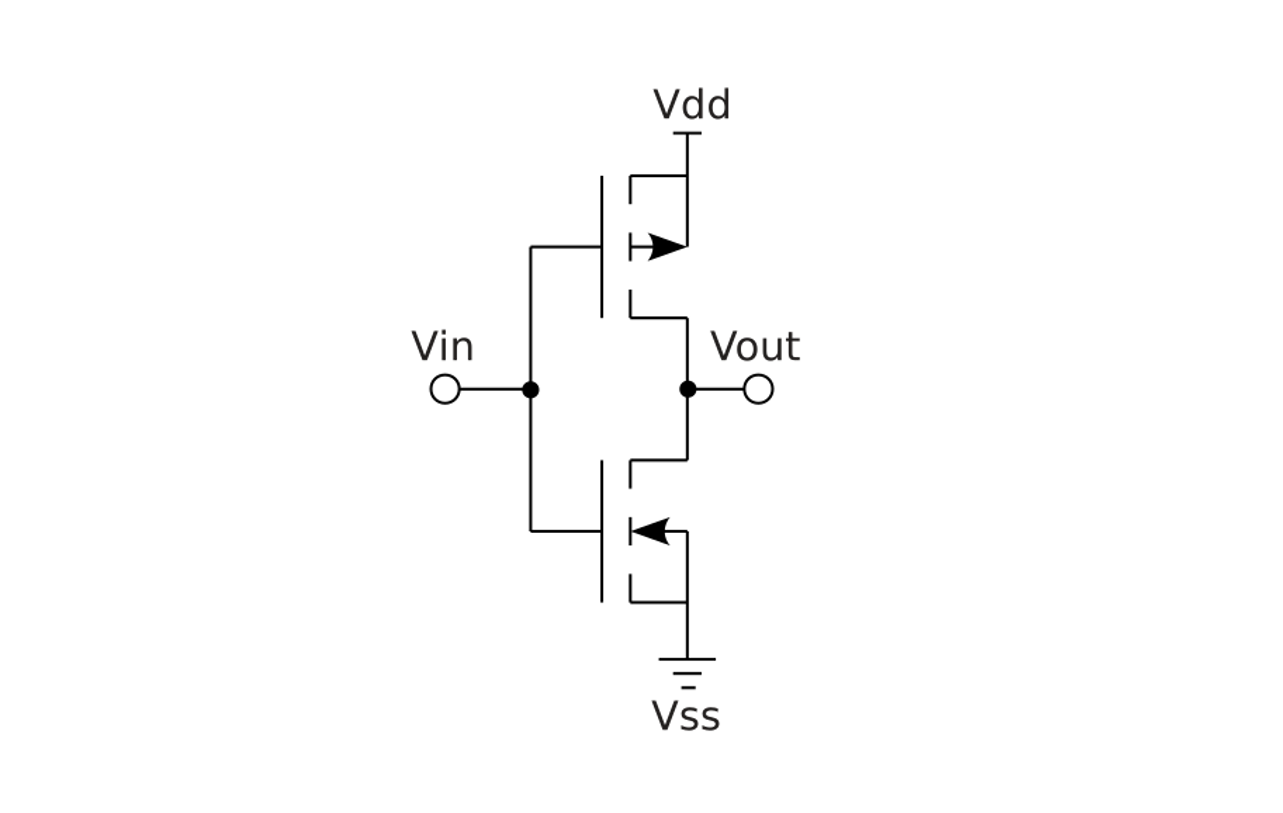

واجهة مستوى CMOS

CMOS (Complementary Metal Oxide Semiconductor) هو مبني على هيكل NMOS و PMOS، وتزويده القياسي بالطاقة هو 5 فولت. على غرار TTL، تم تطوير مستوى LVCMOS كمعيار للمستوى العالي من CMOS، ونظرًا لأن المفاتيح MOS لديها جهد توصيل أقل بالمقارنة مع الثلاثيات القطبية، فإن LVCMOS يمكنه استخدام جهد أقل للاتصال. يتوفر LVCMOS بمستويات 3.3 فولت و 2.5 فولت و 1.8 فولت و 1.5 فولت و 1.2 فولت.

ميزات مستوى (LV) CMOS:

- يتحكم الدائرة CMOS في الأجهزة بواسطة الجهد، وهو بطيء السرعة ويتأخر في نقل البيانات (25-50 نانوثانية)، ولكنه يستهلك القليل من الطاقة. ومع ذلك، عند التبديل بتردد عالٍ، فإن سلسلة CMOS في الواقع تستهلك المزيد من الطاقة بالمقارنة مع TTL.

- يتمتع واجهة CMOS بحدود ضوضاء أكبر مقارنة بواجهة TTL، ومقاومة الدخول أعلى بكثير من مقاومة الدخول لواجهة TTL. في الحالات العادية، يكون استهلاك الطاقة وقدرة مقاومة التشويش في CMOS أفضل بكثير من TTL.

- يحتوي الهيكل الداخلي للدائرة CMOS على هيكل سيليكون قابل للتحكم، وعندما يكون إشارة الإدخال أو الدبوس الداخلي أعلى من قيمة معينة لـ VCC (مثل 0.7 فولت في بعض الشرائح)، وإذا كان التيار كافيًا، فقد يتسبب ذلك في حدوث تأثير القفل وحرق الشريحة.

- مقاومة الدخول لدائرة CMOS عالية جدًا، وبالتالي، يمكن أن تكون سعة التحميل المتصلة بها صغيرة جدًا، ولا يلزم استخدام مكثفات كبيرة. نظرًا لأن دوائر CMOS عادة ما تكون ضعيفة في القدرة على التشغيل، يجب تحويلها إلى TTL قبل تشغيل دائرة ECL. بالإضافة إلى ذلك، عند تصميم دوائر واجهة CMOS، يجب تجنب تحميل السعة القابلة للتحميل بشكل زائد، وإلا فإن زمن الارتفاع سيصبح أبطأ، وسيزداد استهلاك الأجهزة المشغلة (نظرًا لأن السعة القابلة للتحميل لا تستهلك الطاقة).

مقارنة بين المعايير المختلفة للمستوى

تحتوي الدوائر الرقمية على معيار ثنائي العتبة. على الرغم من أنه يتم تمثيله في النهاية بحالتي 0 و 1 فقط، إلا أنه في الدوائر الفعلية، يتم تحديد ما إذا كان الجهد أقل من قيمة معينة يعتبر 0 أما إذا كان الجهد أعلى من قيمة معينة يعتبر 1، من خلال معيار ثنائي العتبة.

| \(VCC\) | \(V_{OH}\) | \(V_{IH}\) | \(V_{IL}\) | \(V_{OL}\) | \(GND\) | |

|---|---|---|---|---|---|---|

| 5V TTL | 5.0 | 2.4 | 2.0 | 0.8 | 0.4 | 0.0 |

| 3.3V LVTTL | 3.3 | 2.4 | 1.5 | 0.8 | 0.4 | 0.0 |

| 5V CMOS | 5.0 | 4.5(0.9*VCC) | 3.5(0.7*VCC) | 1.5(0.3*VCC) | 0.5(0.1*VCC) | 0.0 |

| 3.3V CMOS | 3.3 | 2.97(0.9*VCC) | 2.31(0.7*VCC) | 0.99(0.3*VCC) | 0.33(0.1*VCC) | 0.0 |

| 2.5V CMOS | 2.5 | 2.0 | 1.7 | 0.7 | 0.4 | 0.0 |

| 1.8V CMOS | 1.8 | 1.35 | 1.17 | 0.63 | 0.45 | 0.0 |

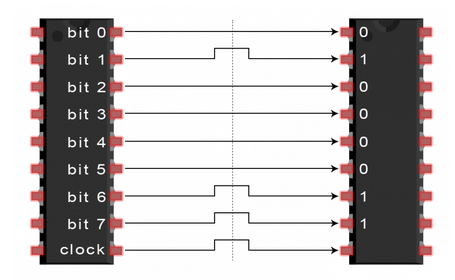

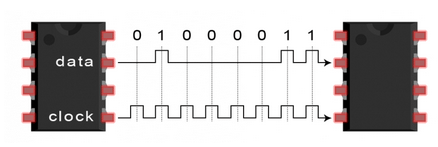

串行与并行通信

数据位可以并行或串行形式传输。在并行通信中,数据位是同时发送的,每个都通过单独的线路。下图是二进制(01000011)中字母 C 的并行传输:

在串行通信中,通过单线逐个发送这些位。下图是字母 C 的串行传输:

参考与致谢

- 《Analog Engineer’s Pocket Reference》

- 一文了解 SPI 总线工作原理、优缺点和应用案例

- [FPGA13][电路]接口电平标准

عنوان النص: https://wiki-power.com/

يتم حماية هذا المقال بموجب اتفاقية CC BY-NC-SA 4.0، يُرجى ذكر المصدر عند إعادة النشر.تمت ترجمة هذه المشاركة باستخدام ChatGPT، يرجى تزويدنا بتعليقاتكم إذا كانت هناك أي حذف أو إهمال.