Fundamentos de Pruebas de Semiconductores - Pruebas Funcionales

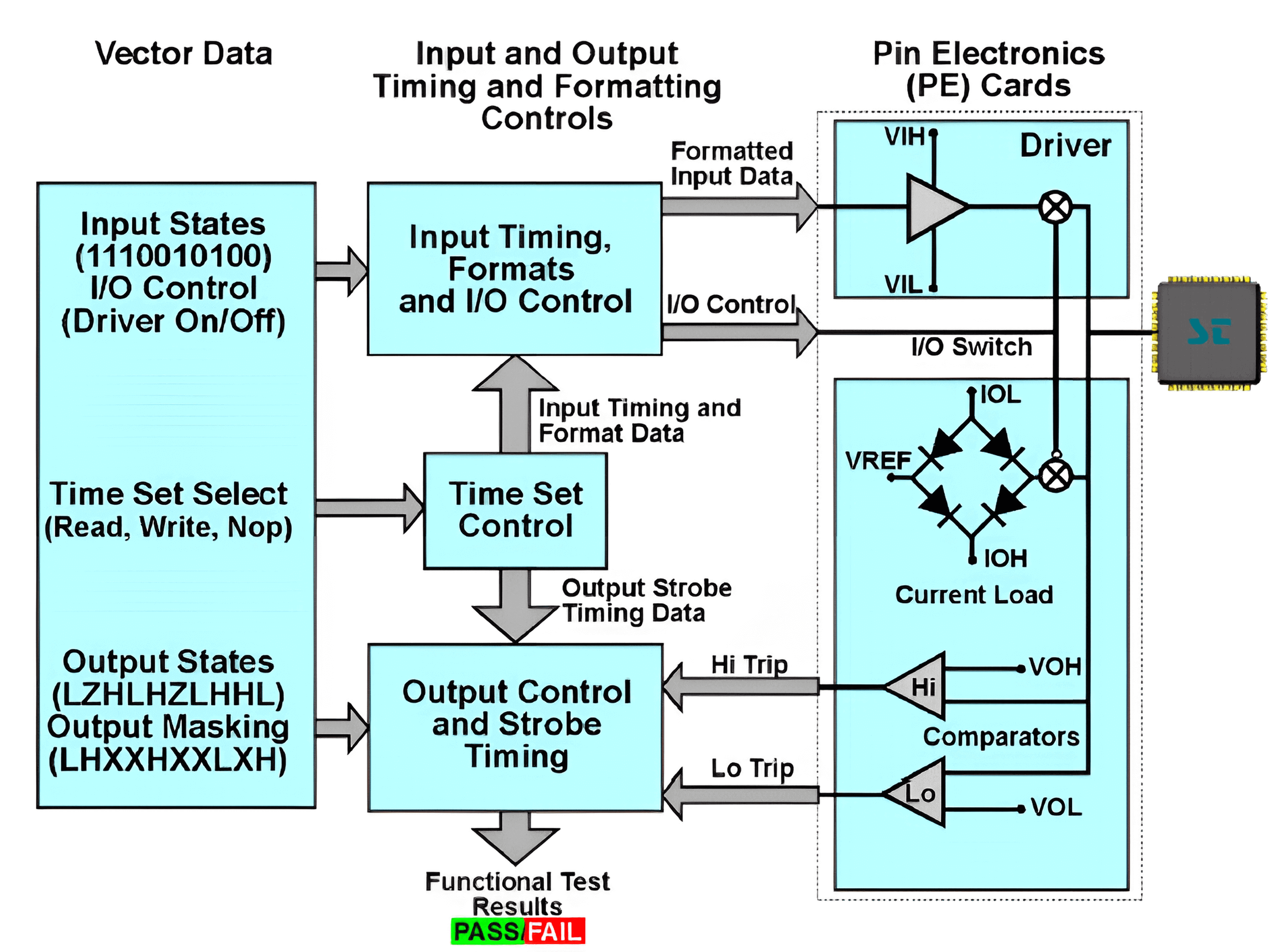

Las pruebas funcionales (Functional Test) se centran en verificar la funcionalidad lógica mediante el uso de vectores de prueba y comandos de prueba. En comparación con las pruebas de corriente continua pura, las pruebas funcionales tienen pasos de combinación más complejos y mayor grado de acoplamiento.

Durante la etapa de pruebas funcionales, el sistema de prueba enviará vectores de prueba al dispositivo bajo prueba (DUT) en intervalos regulares, proporcionando resultados esperados y comparándolos con los datos de salida. Si los resultados reales no coinciden con los valores predichos por los vectores de prueba, se considera una falla.

Conceptos básicos

Vectores de prueba (Test Vectors)

Los vectores de prueba, también conocidos como patrones de prueba (Test Pattern), se pueden entender como la tabla de verdad de entrada y salida de la funcionalidad lógica diseñada para el dispositivo. Los vectores de prueba enfatizan la secuencia temporal y generalmente consisten en una serie de combinaciones de entrada y salida. Por lo general, se utilizan 0/1 para representar niveles de entrada bajo/alto, L/H/Z para representar niveles de salida bajo/alto/estado de alta impedancia, y X para representar la ausencia tanto de entrada como de salida.

Prueba funcional general

Métodos de prueba funcional para varios parámetros

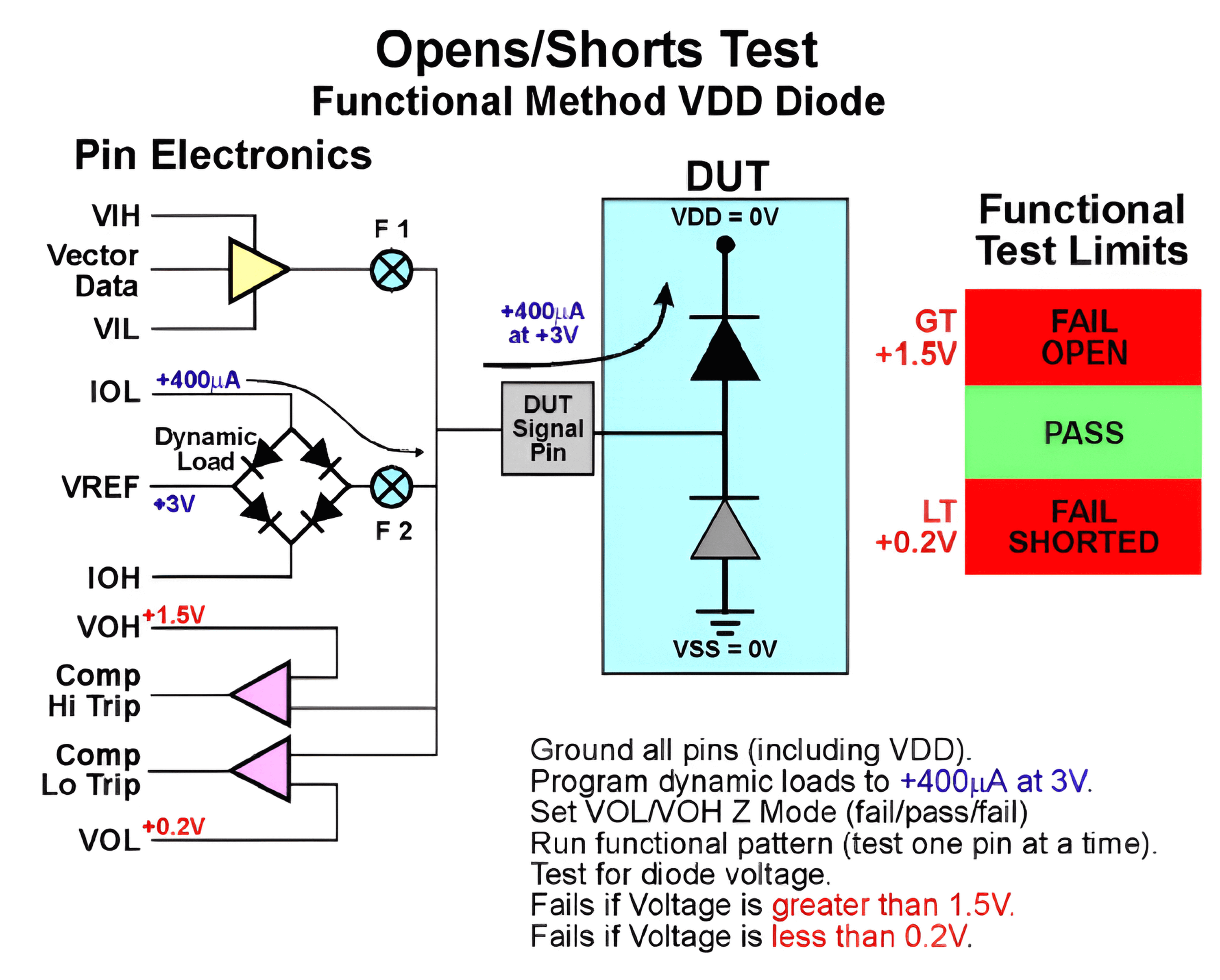

Prueba de OS - Método de prueba funcional

La prueba de cortocircuito y circuito abierto no es una funcionalidad en sí, pero también se puede realizar mediante el método de prueba funcional. Se apaga la PMU (Unidad de Medición de Potencia) y el controlador, y se realiza la prueba utilizando una carga de corriente y un receptor de voltaje. El diagrama de prueba es el siguiente:

El flujo de prueba es el siguiente:

- Conectar a tierra todos los pines excepto el pin bajo prueba (pines de alimentación y señal).

- Definir VOL/VOH (por ejemplo, 0.2V/1.5V).

- Configurar el pin bajo prueba en modo de salida y desconectarlo (estado de alta impedancia Z).

- Proporcionar VREF (3V) para generar una corriente de carga dinámica (aproximadamente 400µA) y medir el voltaje en el pin bajo prueba.

- Si es mayor que VOH (+1.5V): Falla (abierto).

- Si es menor que VOL (+0.2V): Falla (cortocircuito).

- Si está en estado de alta impedancia (caída de voltaje de aproximadamente 0.65V después del sesgo positivo): Aprobado.

- Restablecer el estado del pin y pasar al siguiente pin.

El ejemplo de los vectores de prueba para esta prueba es el siguiente:

00000 /* ciclo 1 Conectar a tierra todos los pines */

Z0000 /* ciclo 2 Probar el diodo de protección del primer pin */

0Z000 /* ciclo 3 Probar el diodo de protección del segundo pin */

00Z00 /* ciclo 4 Probar el diodo de protección del tercer pin */

000Z0 /* ciclo 5 Probar el diodo de protección del cuarto pin */

0000Z /* ciclo 6 Probar el diodo de protección del quinto pin */

/* El siguiente ciclo se ejecutará de forma independiente */

ZZZZZ /* ciclo 7 Desconectar todos los pines y probarlos */

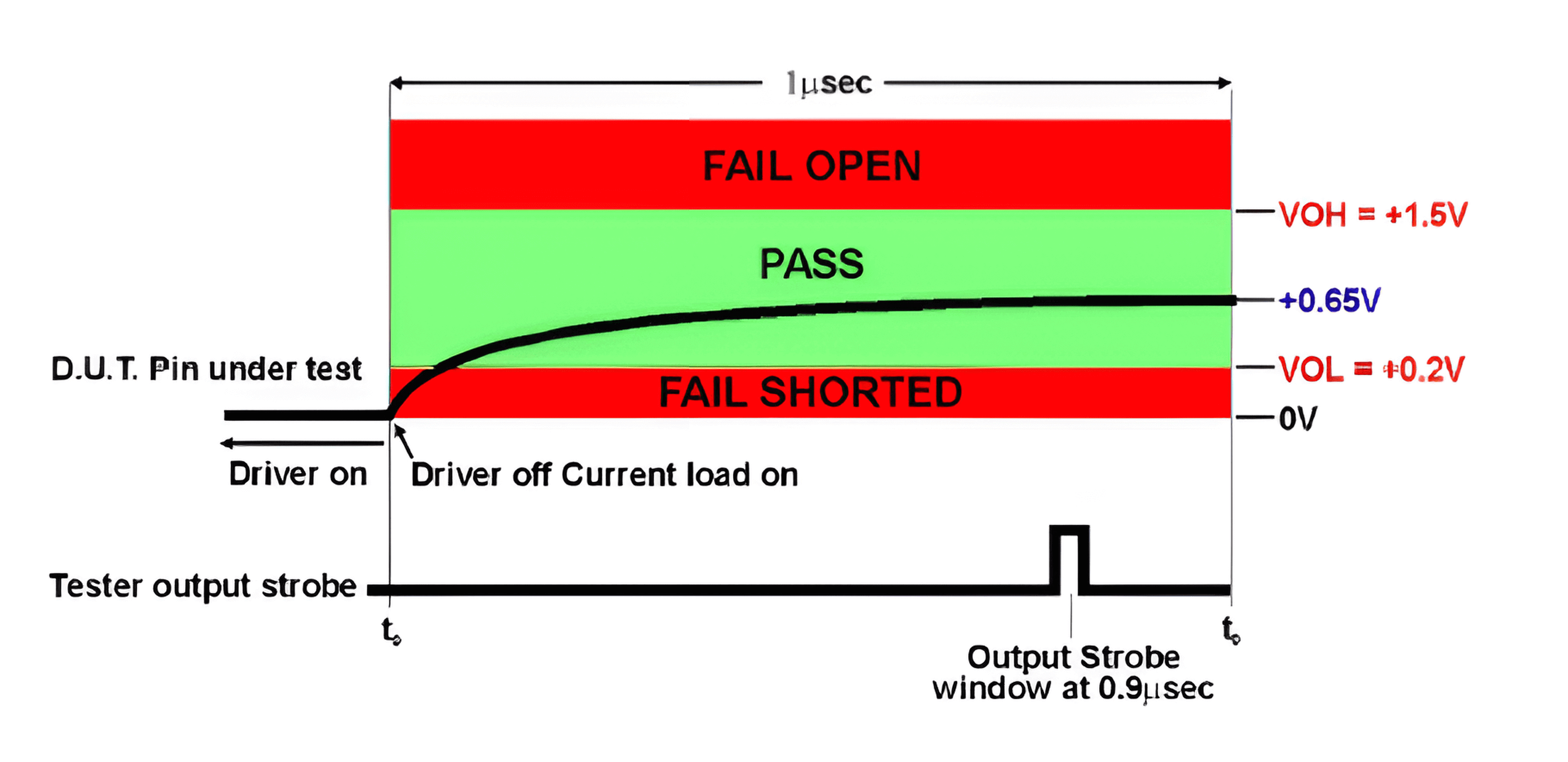

El siguiente diagrama muestra la variación normal del voltaje del pin y la ventana de muestreo. La ventana de muestreo se establece en 0.9µs con una duración de 0.01µs para permitir que el voltaje se estabilice antes de realizar el muestreo:

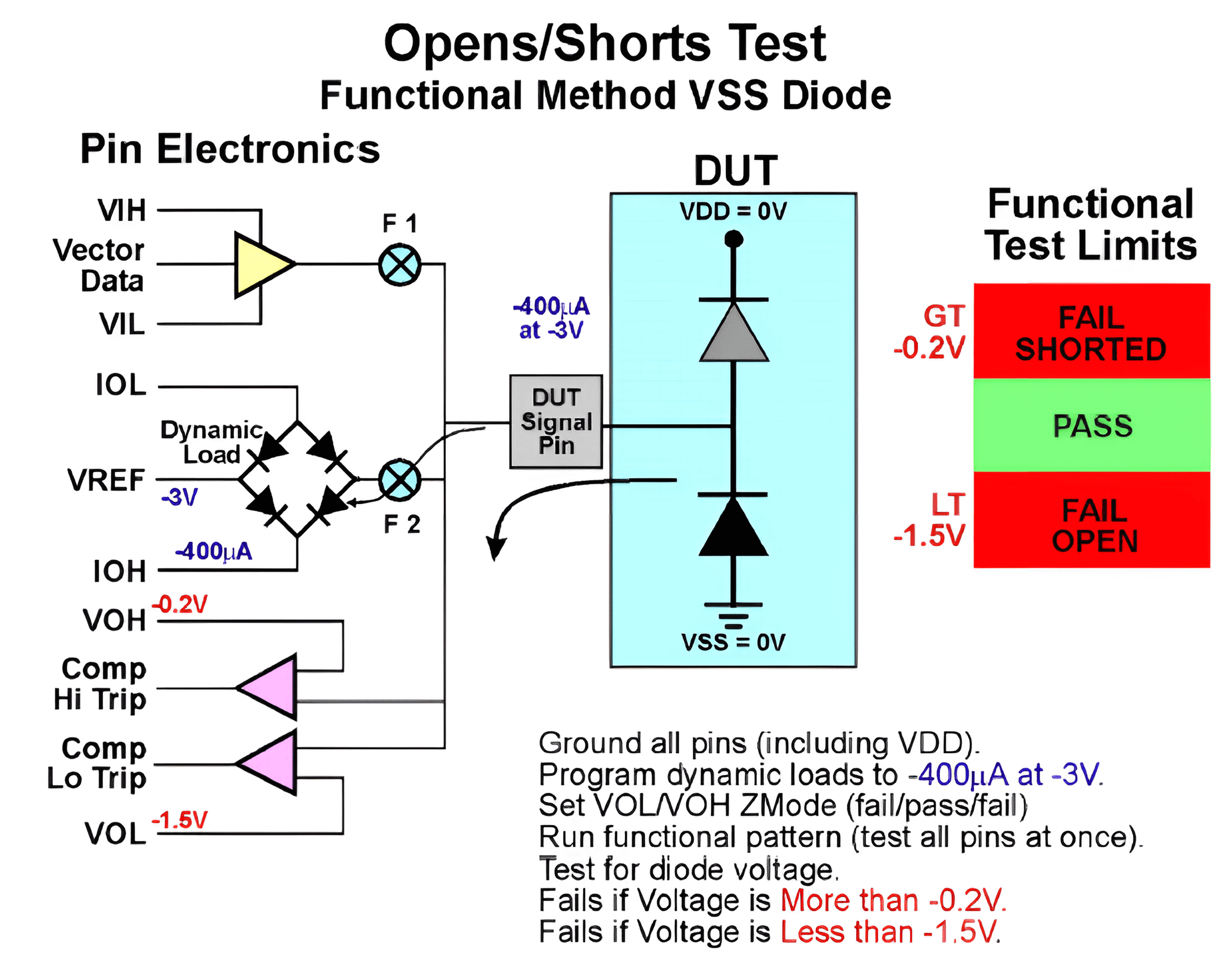

A continuación, se realiza la prueba del diodo de protección a tierra. Solo es necesario verificar si está abierto (si hubiera un cortocircuito, no pasaría la prueba anterior). El siguiente diagrama muestra el método de prueba funcional del diodo de protección a tierra:

Para esta prueba de vectores, solo es necesario ejecutar el ciclo 7 anterior (ZZZZZ) una vez para probar en paralelo todos los diodos de protección a tierra.

(Para conectar el pin a tierra se utiliza DPS; si hay una falla abierta, el voltaje medido será VREF en lugar del voltaje de abrazadera, no confundir con el método de corriente continua).

- 供电 VDDmin(??)。

- 设置 VREF(量程中间值),将形成动态负载电流。

- 执行功能测试,监控引脚的电压

- 低于 VOH Spec 或高于 VOL Spec:Fail

- 高于 VOL Spec:Fail

- 其他区间:Pass

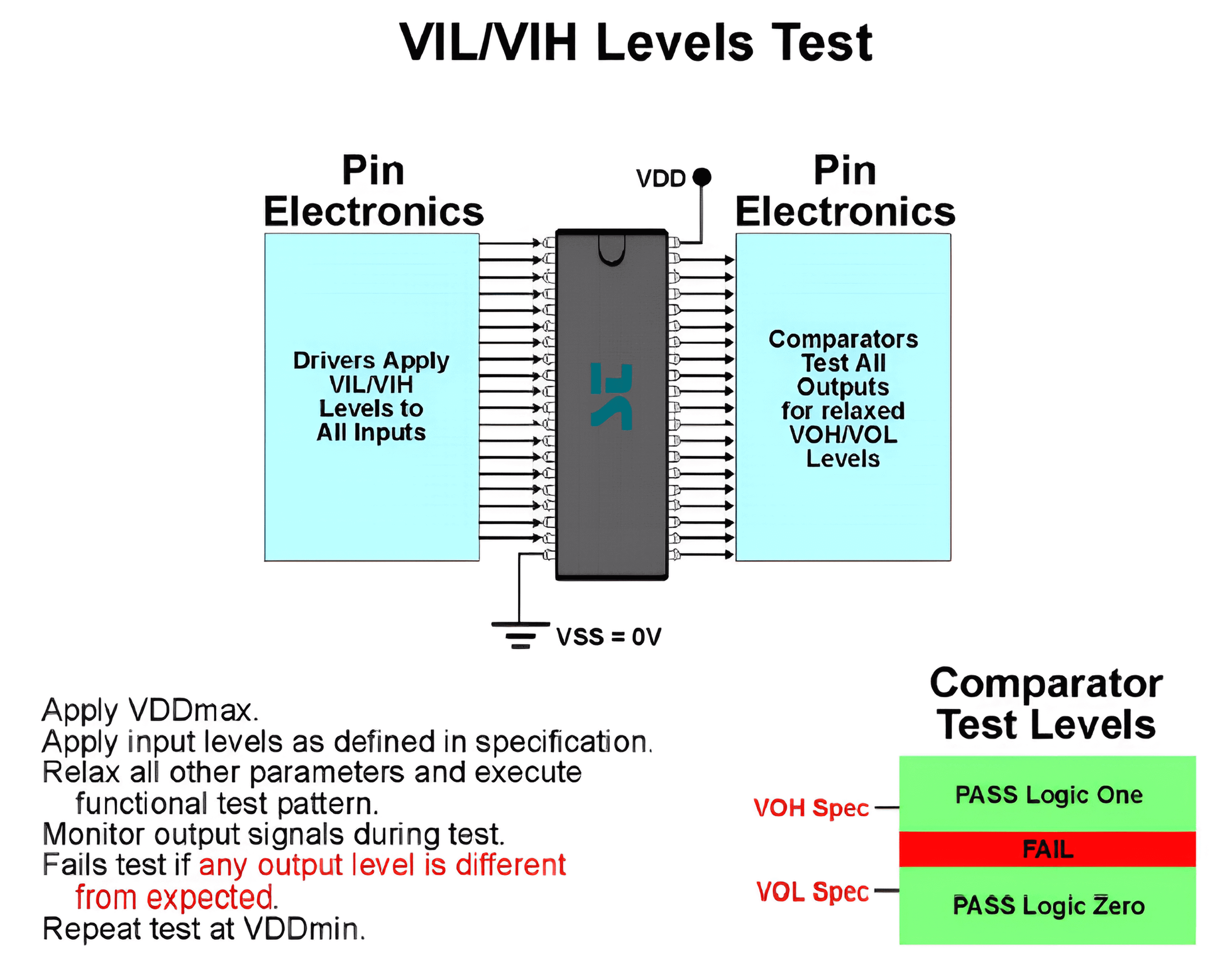

VIL/VIH 测试 - 功能测试法

VIL/VIH es para verificar si el DUT puede reconocer correctamente la lógica de entrada. El diagrama de flujo para medir VIL/VIH utilizando el método de prueba funcional es el siguiente (asumiendo que el lado izquierdo del chip es la entrada y el lado derecho es la salida, con niveles lógicos de entrada y salida en fase):

El proceso para medir VIL/VIH utilizando el método de prueba funcional es el siguiente:

- Primero, se debe suministrar una fuente de alimentación VDDmax al DUT.

- Se aplica el voltaje de entrada nominal VIL/VIH a los pines, asegurando que los demás parámetros cumplan con un margen adecuado.

- Se realiza la prueba funcional y se monitorea el voltaje en los pines de salida.

- Si el voltaje es menor que el valor especificado de VOH: Fail

- Si el voltaje es mayor que el valor especificado de VOL: Fail

- En otros casos: Pass

- Se suministra una fuente de alimentación VDDmin al DUT y se repite el proceso anterior.

Si la prueba no pasa y no se puede identificar el problema, se puede proporcionar un margen adicional para descartar problemas causados por otros factores. Por ejemplo, se puede aplicar un nivel bajo óptimo (0V) para VIL y un nivel alto óptimo (VDD) para VIH, y verificar si la prueba se pasa correctamente siguiendo el proceso, luego se pueden asignar gradualmente los valores originales de VIH/VIL para descartar problemas.

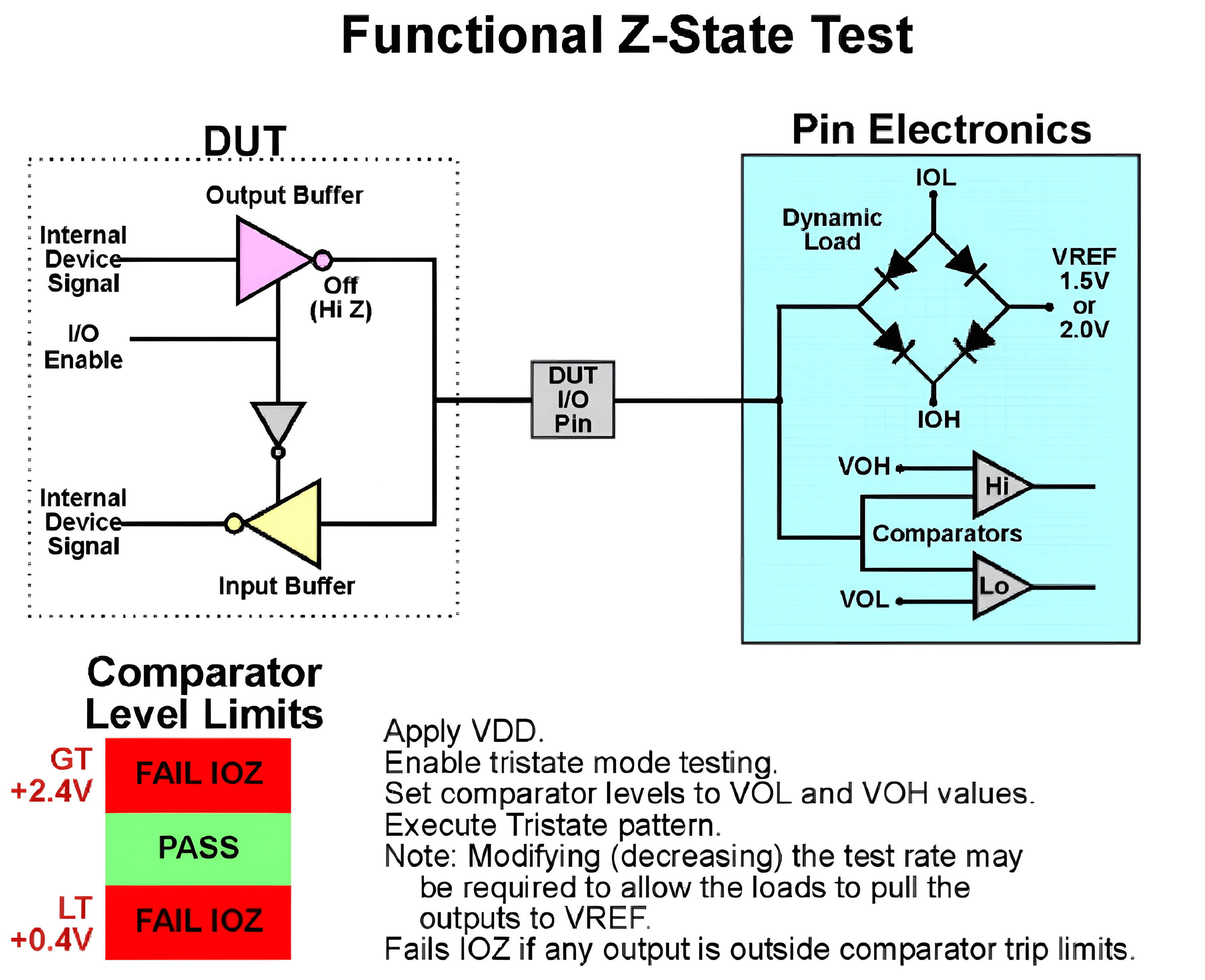

IOZL/IOZH 测试 - 功能测试法

El diagrama de flujo para medir IOZL/IOZH utilizando el método de prueba funcional es el siguiente:

El proceso de prueba es el siguiente:

- Se suministra una fuente de alimentación VDD al DUT y se configura el comparador con los valores VOL/VOH.

- Se configura VREF para generar corriente de carga dinámica y se mide el voltaje en los pines de entrada.

- Si el voltaje es mayor que el valor especificado de VOH: Fail

- Si el voltaje es menor que el valor especificado de VOL: Fail

- En otros casos: Pass

Referencias y Agradecimientos

- "The Fundamentals Of Digital Semiconductor Testing"

- "DC Test Theory"

Dirección original del artículo: https://wiki-power.com/

Este artículo está protegido por la licencia CC BY-NC-SA 4.0. Si desea reproducirlo, por favor indique la fuente.Este post está traducido usando ChatGPT, por favor feedback si hay alguna omisión.