Protocolo de comunicación - Ethernet 🚧

Referencias y agradecimientos

Dirección original del artículo: https://wiki-power.com/ Este artículo está protegido por la licencia CC BY-NC-SA 4.0. Si desea reproducirlo, por favor indique la fuente.

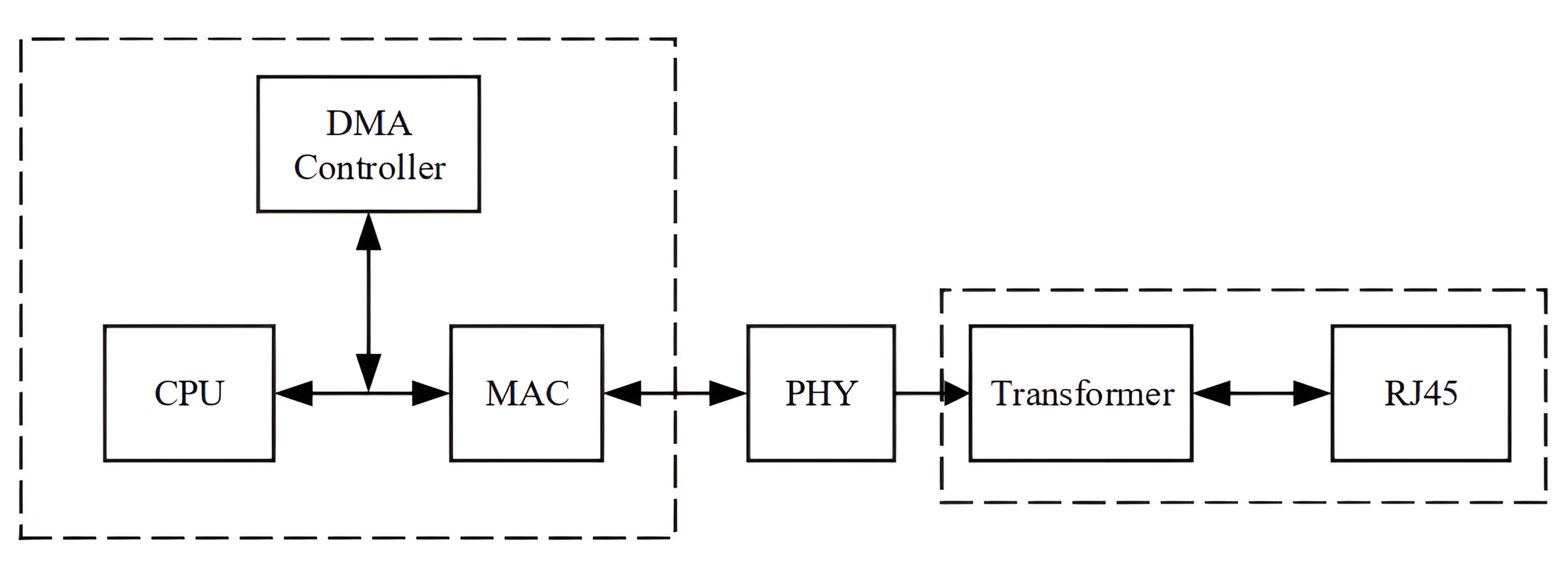

Hardware de Ethernet embebido

El hardware de Ethernet embebido en un sistema embebido está compuesto principalmente por los siguientes componentes: controlador MAC, chip PHY, transformador de red y conector RJ45. Algunos sistemas también pueden incluir un controlador DMA.

Por lo general, la CPU/MCU integra el controlador MAC en el chip (el MAC es un circuito digital y, debido a consideraciones de área de chip y arquitectura, generalmente se integra en el chip), por lo que los componentes que deben diseñarse externamente son el PHY, el transformador y la interfaz. En muchos casos, el transformador de red también se integra en el conector RJ45.

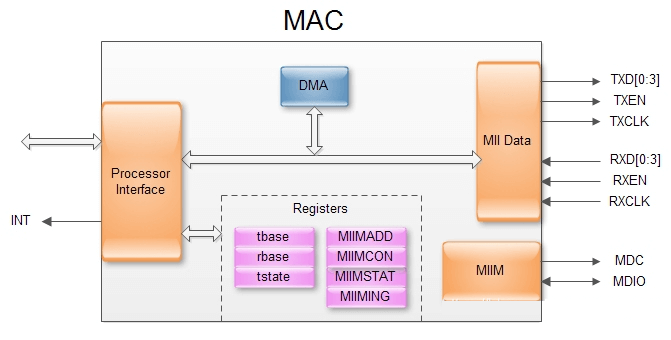

MAC

El MAC (Protocolo de control de acceso al medio, Media Access Control) se encuentra en la capa de enlace de datos de la estructura de siete capas del modelo OSI y es responsable de controlar y conectar el medio físico. El MAC sigue el estándar IEEE-802.3.

Al enviar datos, el protocolo MAC puede determinar de antemano si se pueden enviar datos. Si es posible, agrega información de control a los datos y luego envía los datos y la información de control en un formato especificado a la capa física.

Al recibir datos, el protocolo MAC primero verifica la información de entrada y si se produjeron errores de transmisión. Si no hay errores, elimina la información de control y la envía a la capa LLC.

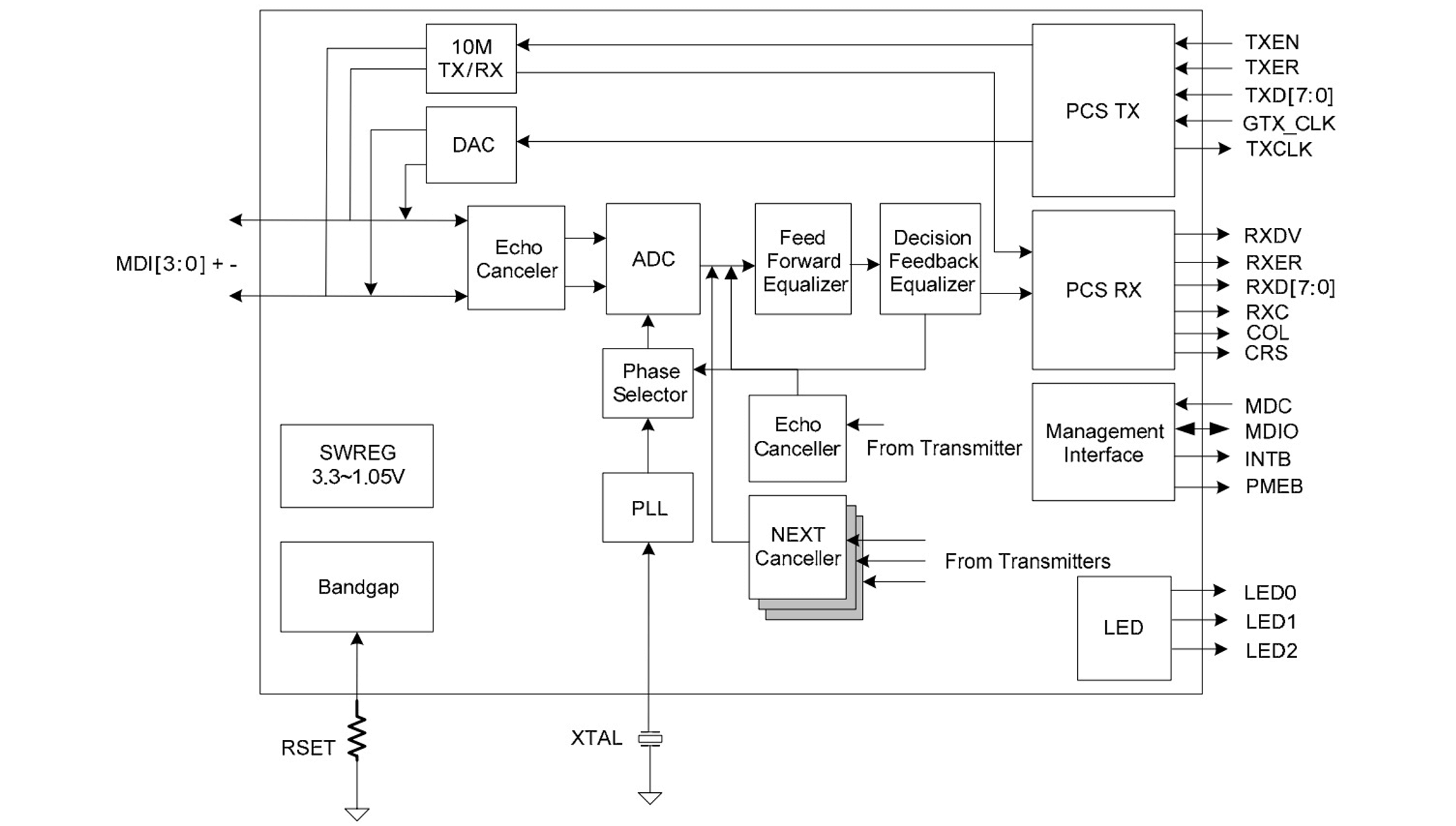

PHY

PHY es el transceptor de interfaz física que implementa la capa física de Ethernet. El PHY está definido por el estándar IEEE-802.3 e incluye la subcapa de interfaz independiente del medio MII/GMII, la subcapa de codificación física PCS, la subcapa de anexo físico PMA, la subcapa relacionada con el medio físico PMD y la subcapa MDI.

Al enviar datos, el PHY recibe los datos transmitidos desde el MAC (para el PHY, no hay concepto de trama, solo datos sin importar la dirección, los datos o el CRC. Para 100BaseTX, debido al uso de codificación 4B/5B, se agrega un código de detección de errores de 1 bit por cada 4 bits), luego convierte los datos paralelos en datos de flujo serie, los codifica según las reglas de codificación de la capa física y los convierte en señales analógicas para enviarlos. El proceso es inverso al recibir datos. A continuación se muestra un diagrama de la estructura interna típica de un PHY (RTL8211E):

Protocolo de interfaz entre MAC y PHY

Este post está traducido usando ChatGPT, por favor feedback si hay alguna omisión.